# **3-Phase 4-wire UPQC Topology with reduced DC-link Voltage** rating for Power Quality Improvement using Fuzzy Controller

Kadali Jagadeesh<sup>1</sup>, Dasari Prasad<sup>2</sup> and Dr.P. Ramesh<sup>3</sup>

<sup>1</sup>M-Tech Scholar Department of EEE, PACE Institute of Technology & Sciences, Ongole, A.P.

<sup>2</sup>Assistant Professor, Department of EEE, PACE Institute of Technology & Sciences, Ongole, Prakasam (dist), A.P., India.

<sup>3</sup>Professor& Head, Department of EEE, PACE Institute of Technology & Sciences, Ongole, A.P., India

<sup>1</sup>k.jgdsh231@gmail.com, <sup>2</sup>prasad.march17@gmail.com, <sup>3</sup>nannu.niky@gmail.com

#### Abstract

Unified power quality conditioner is one of the advanced forms of power conditioning device, which is a combination of back to back connected series APF and shunt active power filter (SAPF) connected to a common DC link voltage. This topology will facilitates this device to have a reduced dc-link voltage without reducing its compensation capability. This device is mainly used in improving the power quality. For the improvement of power quality (PQ) complications in a 3-phase 4-wire distribution system, two topologies are presented. In this paper a four-leg voltage source inverter (VSI) based topology of a four-wire UPQC is discussed in this work. The performance of each topology of this device is evaluated for different PQ problems such as voltage harmonic mitigation, load balancing, source neutral current mitigation, current harmonic mitigation, and power-factor correction. The main purpose this device is to compensate load current and supply voltage imperfections. Converter and control analysis is presented together with the results showing the modes of operation. Detailed design aspect of the series capacitor and VSI parameters has been discussed in this paper. For better power quality improvement the PI controller is replaced by the fuzzy controller and the results are verified. The proposed topology enables UPQC to compensate current harmonics, voltage sags, and voltage swells with a reduced DC-link voltage without reducing its compensation capability by resolving the circuit in MATLAB/SIMULINK software.

**Keywords**: Fuzzy controller, Power quality, UPQC, Load balancing, voltage sags, voltage swells, APF

### 1. Introduction

UPQC topology with reduced DC-link voltage is proposed in this paper. The interfacing inductor of the shunt active filter is connected in series with the capacitor ( $C_f$ ). The series capacitor will enables us in the reduction in DC-link voltage requirement of the shunt active filter and simultaneously it compensates the reactive power required by the load in the system, which will maintain a unity power factor in the system, without compromising the performance of the series capacitor. This will allows us to match the DC-link voltage requirements of both series and shunt active filters in the UPQC device with a common DC-link capacitor. Further, in this topology the neutral of the system will be connected to negative terminal of the DC bus which will avoids the requirement of the fourth leg in VSI of the shunt active filter of UPQC as a result and also enables the independent control of each leg in the shunt VSI of UPQC with a single DC capacitor.

There are different topologies were reported in the literature of three-phase four-wire UPQC which use active compensation for the reduction of source neutral current along with other PO problems. For the reduction of source neutral current, the use of passive elements is advantageous than the active compensation due to less complexity and ruggedness. There are lots of techniques proposed for the compensation of neutral current such as using a star-delta transformer in a three-phase four-wire distribution system and some of these have been limited. The application of star-delta transformer along with an APF is used for the reduction of harmonic current in the neutral conductor. A filter operated with a three single-phase transformers with a capacitor has been used for removing harmonic current from the neutral conductor and has been limited. Another scheme by taking a six-phase system, with the help of two transformers which are connected in anti-phase has been described for canceling third harmonic current in the neutral conductor. The star-delta transformer along with a half-bridge PWM inverter and a diode rectifier is also studied for the compensation of neutral current. For the reduction of source neutral current along with other current based distortions, a combination of readily available three-leg VSI with star-delta transformer has been studied in the literature for 3P-4W DSTATCOM [11, 12]. Unfortunately, for the reduction of neutral current the performance of the star-delta transformers is affected to an amount under unbalanced or distorted source voltages, which is very common in general. The UPQC is one of the key CPDs, which will takes care of both current and voltage based distortions simultaneously. Therefore, for neutral current reduction a combination of star-delta transformer with UPQC is more validated. In this paper, a simple star-delta configuration is utilized for the mitigation of source neutral current, while other options such as Tconnected or zig-zag transformers or T-connected transformer which will require specially designed transformers.

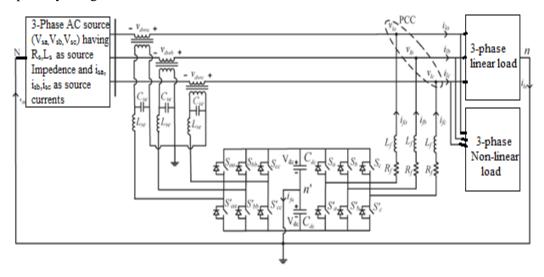

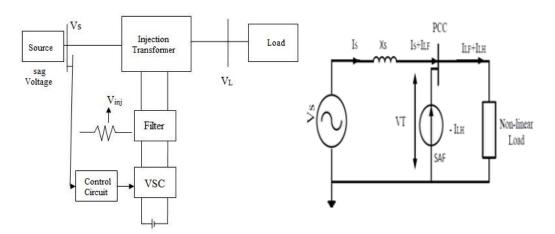

Figure 1. Equivalent Circuit of Neutral-Clamped VSI Topology-based UPQC.

The proposed and conventional topologies of the UPQC are discussed in detail. Figure 1 shows the power circuit of the neutral-clamped VSI topology-based UPQC which is regarded as the conventional topology in this study. Despite of this, this topology will use two dc storage devices, each leg of the VSI will be controlled independently, and tracking will be smooth with less number of switches when compared to other VSI topologies. Here the source voltages of phases a, b, and c, are  $V_{sa}$ ,  $V_{sb}$ , and  $V_{sc}$  respectively. Similarly, terminal voltages are  $V_{ta}$ ,  $V_{tb}$ , and  $V_{tc}$ . The injected voltages of series active filter are  $V_{dvra}$ ,  $V_{dvrb}$ , and  $V_{dvrc}$ . The three phase source currents are shown by  $i_{sa}$ ,  $i_{sb}$ , and  $i_{sc}$ , and load currents are shown by  $i_{la}$ ,  $i_{lb}$ , and  $i_{lc}$ . The shunt active filter currents are represented by  $i_{fa}$ ,

$i_{fb}$ ,  $i_{fc}$ , and  $i_{ln}$  represents the current in the neutral leg.  $R_s$  and  $L_s$  describe the feeder resistance and inductance, respectively. The interfacing resistance and inductance of the shunt active filter are represented by  $R_f$  and  $L_f$ , respectively, and the filter capacitor and the interfacing inductance of the series active filter are represented by  $C_{\rm se}$  and  $L_{\rm se}$ , respectively. The load is having both nonlinear and linear loads as shown in this Figure 1. The dc-link capacitors and the voltages across them are given by  $C_{\rm dc1} = C_{\rm dc2} = C_{\rm dc}$  and  $V_{\rm dc1} = V_{\rm dc2} = V_{\rm dc}$ , respectively, and the total dc-link voltage is given by  $V_{\rm dbus}(V_{\rm dc1} + V_{\rm dc2} = 2V_{\rm dc})$ .

# 2. System Configuration

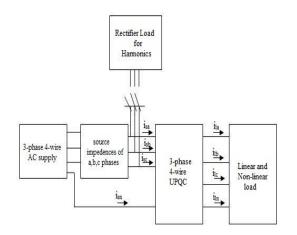

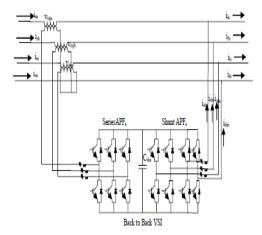

The system under consideration for three-phase, four wire distribution system is shown in Figure 2. The connection of UPQC is made before the load to make the source and the load voltage free from any disturbances. At the same time, the reactive current drawn from the source at source side would be in phase with utility voltages. Supply is made to realize that the voltage harmonics in the source voltage by switching on/off the three-phase diode bridge rectifier. The UPQC, carried on by using two VSIs, is shown in Figure 3: one VSI acts as the series APF and the other as the shunt APF. The shunt APF is performed by using a three-phase, four-leg VSI, and the series APF is carried on by using a three-phase, three-leg VSI. Both APFs are shares a common dc link between them. The four-leg, VSI based shunt active filter is having a capability of load balancing, mitigating the harmonics in the source currents, power-factor correction and negative sequence of the source current.

Figure 2. Three-phase, Four Wire Distribution System

Figure 3. UPQC Carried Out by using Two VSIs

# 3. Three Phase Four Wire UPQC

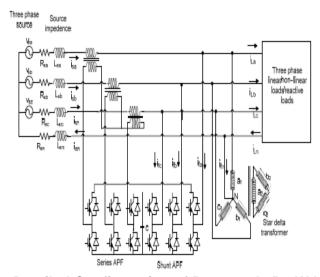

Figure 4 shows a 3P-4W UPQC topology, which is feeds a combination of non-linear and linear unbalanced load. The shunt and series APFs are being realized by using two readily available three-leg VSIs. The dc links of both APFs has been connected to a common dc link capacitor. The series APF is being connected in between the supply and load terminals using three single phase transformers which having a turn's ratio of 5:1. The primary windings of these transformers are star connected and the secondary windings have connected in series with the three-phase supply. In addition to this it provides the required injecting voltages, these transformers are also used to filter the switching ripple content in the series APF. A small capacity rated R-C filter has connected in parallel with the secondary of each series transformer is to eliminate the high switching ripple content in the series APF injected voltages. The voltage source inverters for both the APFs are implemented by using Insulated gate Bipolar Transistors (IGBTs). In Fig.1 ( $i_{fa}$ ,  $i_{fb}$ ,  $i_{fc}$ ), ( $i_{sa}$ ,  $i_{sb}$ ,  $i_{sc}$ ), and ( $i_{la}$ ,  $i_{lb}$ ,  $i_{lc}$ ) represents the shunt APF currents, load currents and source currents in phases a, b and c respectively.

The load neutral current, source neutral current, and neutral current of the additional connected transformers are being shown by  $i_{ln}$ ,  $i_{sn}$  and  $i_{Tn}$ , respectively. The injected voltages by the series APF's in phase a, b and c are given by  $V_{inja}$ ,  $V_{injb}$  and  $V_{injc}$ , respectively. In this topology, a star-delta transformer is being connected in shunt near the load for the reduction of the source neutral current. The delta connected secondary will give us a circulating path to the zero sequence current  $(i_o)$  in case of unbalanced load and hence the supply neutral current will be reduced to zero. The load under consideration is having a combination of non-linear and linear loads. Two single-phase R-L loads are taken as unbalanced linear load, where as a three-phase diode bridge rectifier with a resistive load on dc side will considered as a non-linear load.

Figure 4. Detailed Configuration of Proposed 3P-4W UPQC.

#### **Series Active Filter**

Dynamic Voltage Restorer is one of custom power device mainly used for maintaining the load voltage at constant in the distribution system. DVR is having two operating modes. In normal operating mode it is in standby mode in which voltage injection is zero by DVR. Most of the time DVR will be in standby mode and hence it reduces the losses, As soon as control circuit will detects the any voltage disturbance, reference voltage will be generated for a required magnitude, duration and phase is injected through the

injection transformer. This mode of DVR is called as injecting mode. This injection should satisfy the following equation

$$V_L = V_S + V_{INJ}$$

Where  $V_S$  will be the source voltage,  $V_{INJ}$  will be the injected voltage by DVR and  $V_L$  will be the load voltage. Fig 5 shows the basic configuration and operation of DVR which having an injection transformer, Voltage Source Converter (VSC), storage device, control system and harmonic filter.

#### **Shunt Active Filter**

In general nonlinear loads will require harmonic current  $I_{LH}$  from the main supply along with a fundamental current  $I_{LF}$ . This causes the main supply to operate at a frequency above the normal 50Hz or 60Hz and by doing, it will create a negative phase-sequence component which is not needed.

The shunt active filter will be considered as a current source element because it injects non-sinusoidal current  $I_{LH}$  through the parallel branch of the network in order to minimize the current harmonic demand of the nonlinear load. The role of the active filter controller is to sense and watch the load currents and to suitably determine the correct reference harmonic current for the inverter. Once the correct reference harmonic content is found; this reference current is fed through a suitable current controller and then it will sent to the inverter for the injection into the network. Figure 6 .shows the principle of shunt active filter and its basic concept.

Figure 5. Structure of DVR Figure 6. Principle of Shunt Sctive filter

## 4. Fuzzy Controller

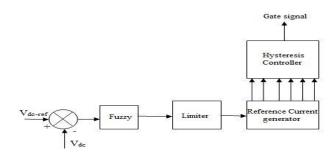

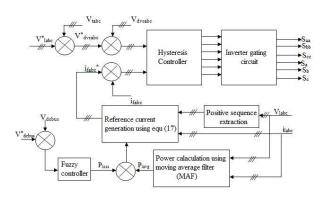

The internal structure of the control circuit of fuzzy is shown in Figure 7. The control scheme will consists of limiter, Fuzzy controller, and three phase sine wave generator which generates reference current and switching signals. The peak value of reference currents will be estimated by regulating the DC link voltage. The actual capacitor voltage will be compared with a set of reference values. The error signal is then processed over a Fuzzy controller, which contributes to zero steady error in tracking the reference current signal.

A fuzzy controller will convert a linguistic control strategy into an automatic control strategy, and fuzzy rules are constructed by expert or experience in knowledge database.

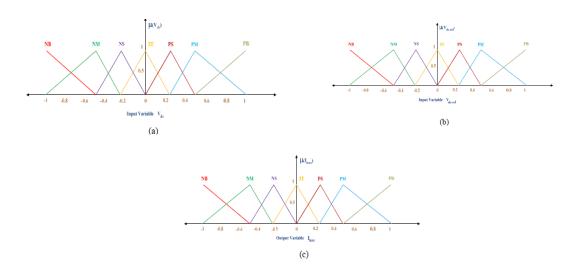

Firstly, the input reference voltage  $V_{\text{dc-ref}}$  and the input voltage  $V_{\text{dc}}$  have been placed of the angular velocity to be the input variables of the fuzzy logic controller. Then the output variable of the fuzzy logic controller will be presented by the control Current  $I_{\text{max}}$ . To convert these numerical variables into linguistic variables, the following seven fuzzy levels or sets are chosen as: ZE (zero), PS (positive small), PM (positive medium), PB (positive big) NB (negative big), NM (negative medium), and NS (negative small), as shown in Figure 8.

Figure 7. Conventional Fuzzy Controller.

Figure 8. (a) Input  $V_{dc}$  Normalized Membership Function; (b) Input  $V_{dc-ref}$  Normalized Membership Function; (c) Output  $I_{max}$  Normalized Membership Function.

$\mathbf{E}$ NL NM NS  $\mathbf{E}\mathbf{Z}$ **PS PM** PL Δe NL NLNL NL NMNS EZ NL NM NL NL NL NM NS ΕZ PS NM EΖ PS **PM** NS NL NL NS ΕZ  $\mathbf{E}\mathbf{Z}$ NL NM NS PS PM PL PS NM NS EZPS PM PL PL **PM** NS EΖ PS PM PL PL PL NL NM NS EΖ PS PM PL PL

Table 1: Rule base

# 5. Results and Discussions

The performance of the proposed control strategy was evaluated by computer simulation using Matlab/Simulink Platform. Here simulation is carried out in different cases;

- 1. Conventional converter with PI controller.

- 2. Proposed converter with fuzzy controller.

#### Case-1 Conventional converter with PI controller:

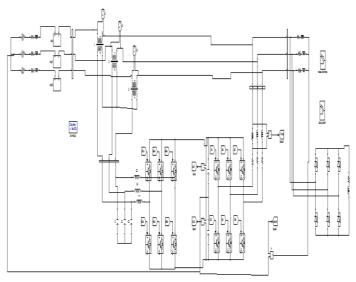

Figure 9. Shows Matlab/Simulink Model of Conventional Model.

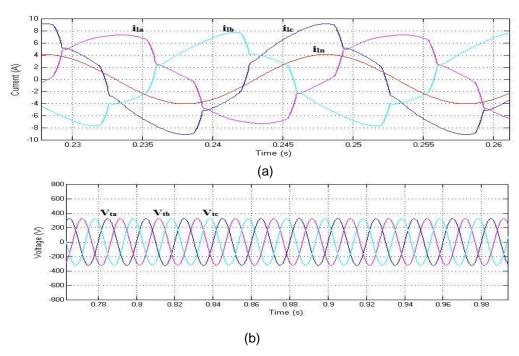

Figure 10. Simulation Results before Compensation (a) Load Currents (b)

Terminal Voltages

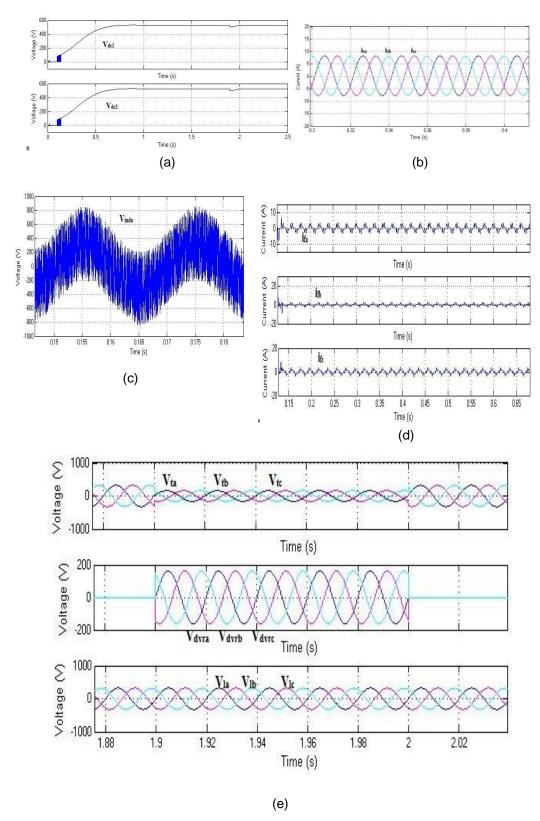

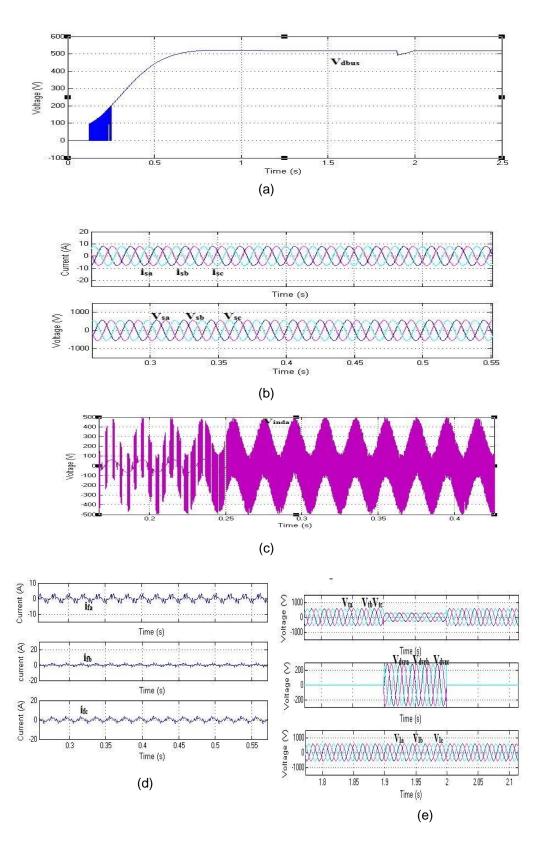

Figure 11. Simulation Results using Conventional Topology (a) DC Capacitor Voltages (top and bottom) (b) Source currents after compensation (c) Voltage across the interfacing inductor in phase-a of the

# shunt active filter (d) Shunt active filter currents (e) Terminal voltages with sag, DVR injected voltages and load voltages after compensation

# Case-2. Control Circuit for Proposed Converter with Fuzzy Controller:

Figure 12. Shows the Control Model of Proposed Converter with Fuzzy Controller.

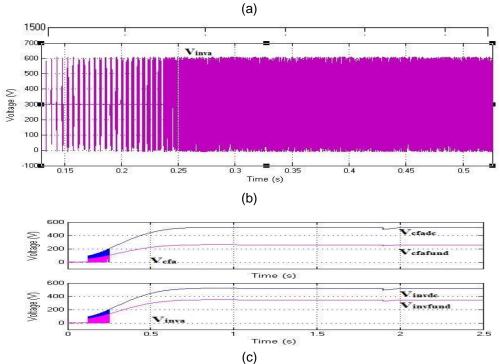

Figure 13. Simulation results with modified topology (a) Voltage across series capacitor and load voltage in phase - a (b) Inverter output voltage in leg – a of shunt active filter (c) FFT of the voltage across series capacitor and inverter output voltage.

Figure 14. Simulation results using modified topology (a) DC capacitor voltages (b) Source currents after compensation (c) Voltage across the interfacing inductor in phase-a of the shunt active filter (d) Shunt active filter currents (e) Terminal voltages with sag, DVR injected voltages and load voltages after compensation.

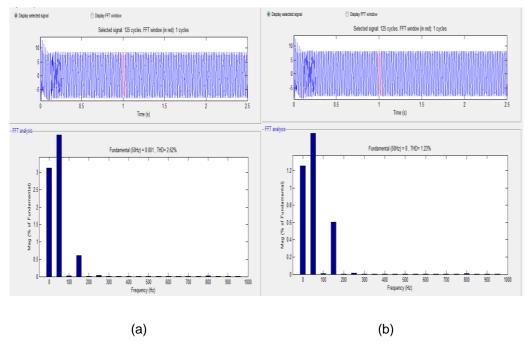

Figure 15. Shows the FFT Analysis of (a) Source Current PI Controller THD Value is 2.62%, (b) Source Current with Fuzzy Controller THD Value is 1.23%.

The source current in the conventional topology is having more distortions compared with the proposed topology. The load voltages and voltages injected by the DVR in the proposed topology are improved compared with the conventional topology. The source current in the proposed topology is having less distortion compared to the conventional. The settling time and rise time is improved in proposed topology. Finally The THD is improved with the fuzzy controller which improves power quality as a result.

# 6. Conclusion

UPQC topology have been proposed in this paper which having the capability to compensate the voltage swells, voltage sags and current harmonics at the load at a lower DC-link voltage by using different control strategies for series and shunt APF's. The proposed method is validated through MATLAB simulation. The topology gives the advantages of both the neutral clamped topology and the four leg topology. THD's are lesser in the source currents.

#### References

- [1] S. B. Karanki, "A Modified Three-phase Four Wire UPQC Topology with Reduced DC-link Voltage Rating" IEEE published on (2011).

- [2] P. Ramesh, G. Ramesh and P. Vyshnavi devi, "Identification and elimination of fault occurrence in sub system by using Resistance switching for linear loads through DSTATCOM", International journal of advanced science and technology, vol. 57, (2013) Aug.

- [3] M. Kesler and E. Ozdemir, "Synchronous-reference-frame-based control method for UPQC under unbalanced and distorted load conditions", IEEE Transactions on Industrial Electronics, vol. 58, no. 9, (2011), Sept., pp. 3967-3975.

- [4] B. Singh and J. Solanki, "Load compensation for diesel generator-based isolated generation system employing DSTATCOM", IEEE Transactions on Industrial Electronics, vol. 47, no. 1, pp. 238 –244, (2011) Jan.-Feb.

- [5] S. Srikanthan and M. K. Mishra, "DC capacitor voltage equalization in neutral clamped inverters for DSTATCOM application", IEEE Transactions on Industrial Electronics, vol. 57, no. 8, (2010) Aug., pp. 2768 –2775.

- [6] R. Gupta, A. Ghosh and A. Joshi, "Multiband hysteresis modulation and switching characterization for sliding-mode-controlled cascaded multilevel inverter", IEEE Transactions on Industrial Electronics, vol. 57, no. 7, (2010) July, pp. 2344 –2353.

- [7] S. Pattanaik and K. Mahapatra, "Power loss estimation for PWM and soft-switching inverter using RDCLI", in International MultiConference of Engineers and Computer Scientists, (2010), pp. 1401– 1406.

- [8] R. Gupta, A. Ghosh, and A. Joshi, "Characteristic analysis for multisampled digital implementation of fixed-switching-frequency closed-loop modulation of voltage-source inverter", IEEE Transactions on Industrial Electronics, vol. 56, no. 7, (2009) July, pp. 2382 -2392.

- [9] R. Gupta, A. Ghosh, and A. Joshi, "Switching characterization of cascaded multilevel-inverter-controlled systems", IEEE Transactions on Industrial Electronics, vol. 55, no. 3, (2008) March, pp. 1047-1058.

- [10] U. K. Rao, M. K. Mishra and A. Ghosh, "Control strategies for load compensation using instantaneous symmetrical component theory under different supply voltages", IEEE Transactions on Power Delivery, vol. 23, no. 4, (2008), pp. 2310-2317.

- [11] H. Suryanarayana and M. K. Mishra, "Fuzzy Logic based Supervision of DC link PI Control in a DSTATCOM", IEEE published on (2008).

- [12] S. V. R. Kumar and S. S. Nagaraju, "Simulation of DSTATCOM and DVR in Power Systems", ARPN Journal of Engineering and Applied Science, vol. 2, no. 3, (2007), pp. 7–13.

- [13] Y. W. Li, D. Mahinda Vilathgamuwa, F. Blaabjerg and P. C. Loh, "A robust control scheme for medium-voltage-level DVR implementation", IEEE Transactions on Industrial Electronics, vol. 54, no. 4, (2007) Aug., pp. 2249-2261.

#### **Authors**

**Kadali Jagadeesh**, He received his B.Tech degree from QIS College of Engineering and Technology, Ongole, India in 2012.

**D.Prasad**, He received the B.Tech degree in EEE from Narasaraopeta Engineering college, Narasarao pet, India, in 2005 and M.Tech. degree in Power Electronics from NIT Calicut in 2008. Currently working as Associate Professor in the Department of Electrical & Electronics Engineering, PACE Institute of Technology & Sciences, Ongole.

**P.Ramesh**, He received B Tech, M tech degree and PhD in Electrical & Electronics Engineering. Currently he is a professor and head of electrical & electronics engineering Department at PACE Institute of Technology& Sciences, Ongole, AP, India. He has published many technical papers in various international journals. He is a corporate member of the Institute of engineers, life member in Indian society of technical education and also member in association of international engineers, society of computer science and information technology. His area of research includes special machines, power and energy, soft computing and power electronics applications.