# A Novel Approach for Dynamic Message ID Allocation in Application Specific can Architecture

Maandvi Sharma<sup>1</sup> and Navdeep Prashar<sup>2</sup>

Bahra University, Shimla Hills India<sup>1</sup> and Assistant Professor Bahra University, Shimla Hills India<sup>2</sup> maandvisharma@gmail.com<sup>1</sup>, nav.prashar@gmail.com<sup>2</sup>

### Abstract

Scheduling messages on the controller area network (CAN) corresponds to assigning identifiers (ID's) to messages according to their priorities. This paper presents a technique of dynamic scheduling in cars using CAN architecture. Static scheduling Id allocation method has several problems like delay, starvation and less accuracy. To overcome these problems the Dynamic approach of message id allocation from message id window is proposed in this paper, which increases the randomness and decreases the biasness by dynamically changing priorities in a CAN network. CAN based architecture is presented and design is implemented using Xilinx device.

Keywords: CAN Bus Arbitration, Dynamic Message Scheduling

# **1. Introduction**

CAN stands for Control Area Network is a serial communications protocol developed by Bosch within the early Eighties, Which efficiently supports distributed real time control within a very high level of security [1]. It defines a regular for economical and reliable communication between detector, controller, actuator and different nodes in period of time applications.

It is the de facto customary during a giant form of networked embedded management systems. The first development was primarily supported by the vehicle industry: which is found during the form of cars, trucks, boats, spacecraft, and different kinds of vehicles [2]. The protocol is additionally wide used these days in industrial automation and different areas of networked embedded management, with applications in numerous products like production machinery, medical instrumentality, building automation, weaving machines, and wheelchairs [1].

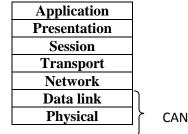

The will protocol standardizes the physical and electric circuit layers, that square measure the second lowest layers of the open systems interconnect communication model. For many systems, higher-layer protocols square measure required to modify economical development and operation [3]. Such protocols square measure required for outlining however they will protocol ought to be employed in applications, as an example, a way to talk to the configuration of identifiers with relation to application messages, a way to package application messages into frames, and the way to affect start-up and fault handling

This paper is organized as follows. Section 2: Introduces CAN bus description. Section 3: Describes message formats and bus arbitration Section 4: Describe proposed framework Section 5: Discuss simulation and result. Section 6: conclusion.

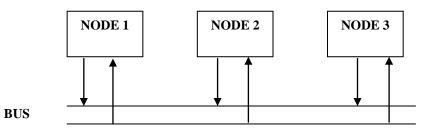

# 2. CAN Bus Description

A bus node specification defines the protocols for the physical and also the electric circuit layers that modify the communication between the network nodes. The frame

consists of a knowledge field and overhead, like symbol and management fields [4]. For CAN, it's supported a non-destructive arbitration method. The will protocol thus belongs to the category of protocols denoted as carrier sense multiple access/collision shunning, which implies that the protocol listens to the network so as to avoid collisions[5]. CSMA/CD protocols like local area network have instead a mechanism to affect collisions once they're detected. It can also include numerous strategies for error detection and error handling. The communication rate of a network supported will depends on the physical distances between the nodes. If the gap is a smaller amount than forty m, the speed is up to one Mbps.

Figure 1. Shows CAN Communication Layers

### 2.1 Message Formats

CAN distinguishes four message formats: information, remote, error, and overload frames. Here we tend to limit the discussion to info frame [10]. The knowledge frame begins with the start-of-frame bit (SOF). It's followed by associate eleven-bit symbol and also the remote transmission request bit (RTR). The symbol and also the RTR bit kind the arbitration field [6]. The management field consists of six bits and indicates what percentage bytes of information follow within the data field. The info field is zero to eight bytes. The info field is followed by the cyclic redundancy (CRC) verification field that permits the receiver to envision if the received bit sequence was corrupted [7]. The two-bit acknowledgment field (ACK) is employed by the transmitter to receive associate acknowledgment of a legitimate frame from any receiver

| S<br>O<br>F | 11-Bit<br>Identi<br>fier | S<br>R<br>R | I<br>D<br>E | 18-Bit<br>Identif<br>ier | R<br>T<br>R | r 1 | r 0 | DLC | 0-8<br>Bytes<br>data | CRC | ACK | E<br>O<br>F | I<br>F<br>S |  |

|-------------|--------------------------|-------------|-------------|--------------------------|-------------|-----|-----|-----|----------------------|-----|-----|-------------|-------------|--|

|-------------|--------------------------|-------------|-------------|--------------------------|-------------|-----|-----|-----|----------------------|-----|-----|-------------|-------------|--|

# 2.2 Bus Arbitration

Arbitration is that the mechanism that handles bus access conflicts. Whenever the will bus is free, any unit will begin to transmit a message [8]. attainable conflicts, as a result of quite one unit getting down to transmit at the same time, square measure resolved by bitwise arbitration victimization the symbol of every unit[8]. Throughout the arbitration section, every transmission unit transmits its symbol and compares it with the extent monitored on the bus [9]. If these levels square measure equal, the unit continues to transmit

Figure 3. Shows CAN Message Frame

# **3. Proposed Framework**

The problem of message scheduling in Control Area Network can be solved by simply making the ids correspond to every message dynamic. This simply means that with every message the id window changes with every message. These message ids selected from a pre defined message id window. The selection of message ids from that window is also dynamic, means there is no fixed order of selection. So that any id can request the bus access any time can have random id, if they are not a part of emergency messages. Besides this if any message belongs to emergency message category then it must be given access as soon as it is available or enabled.

| Id1 | Id2 | Id3 | Id4 | Id5 | Id6 |

|-----|-----|-----|-----|-----|-----|

|     |     |     |     |     |     |

### Figure 4. Shows Message Id Window

Figure 4 shows the message id window from where the ids are fetched randomly and are different for every type of applications for arbitration.

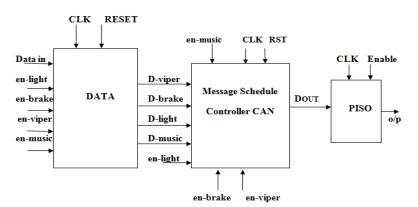

Figure 5. Block Diagram of Proposed Work

Figure 5 shows block diagram of proposed work in which example of a car is considered.

If two or more applications trying to access bus at the same time, then according to "**Dynamic message algorithm**" the one who wins the priority can access the bus first, because multi-priority-window is provided to each application

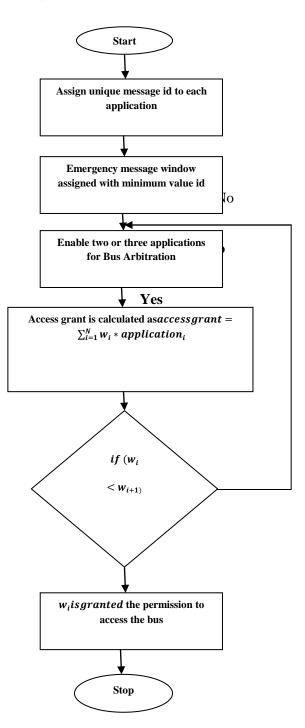

#### **3.1 Flow Diagram of Proposed Framework**

Figure 6. Flow Diagram of Proposed Framework

#### 3.2 Pseudo Code

- 1: Start

- 2: Assign each application a unique message id from id window

- 3: Emergency messages are assigned with minimum id (decimal value)

4: Enable 2 or 3 applications to check bus arbitration (assigned ids act as weights to the equation

$$access grant = \sum_{i=1}^{N} w_i * application_i$$

5: Check for weights for the selected enables

6: *if*  $(w_i < w_{i+1})$   $i \in N\{..\}$  (covers both normal and emergency messages)

$w_i$  is granted the permission to access the bus

8: End

# 4. Results and Simulations

The proposed methodology is simulated using the Xilinx Virtex4 FPGA in Xilinx ISim and the coding is done in Xilinx ISE environment using VHDL language. Table 1 shows the device utilization summary of SPARTAN 3 using dynamic algorithm.

### Table 1. Hardware Utilization Summary

| Logic                      | Used | Available |  |  |

|----------------------------|------|-----------|--|--|

| Number of Slices           | 144  | 768       |  |  |

| Number of Slice Flip Flops | 155  | 1536      |  |  |

| Number of 4 input LUTs     | 254  | 1536      |  |  |

| Number of Bonded IOs       | 42   | 124       |  |  |

| Number of GCLKs            | 1    | 8         |  |  |

### 4.1 Comparison of Proposed Work with Previous Work

### Table 2. Comparison Table of Present Work with Previous Reference Paper

| Logic                      | Proposed | Basic  |  |  |

|----------------------------|----------|--------|--|--|

| Number of Slices           | 144      | 323    |  |  |

| Number of Slice Flip Flops | 155      | 271    |  |  |

| Number of 4 input LUTs     | 254      | 582    |  |  |

| Number of Bonded IOs       | 42       | 42     |  |  |

| Number of GCLKs            | 1        | 1      |  |  |

| Delay (ns)                 | 8.218    | 9.010  |  |  |

| Frequency (MHz)            | 121.68   | 110.98 |  |  |

| Power (mW)                 | 6.18     | 19.06  |  |  |

From Table 2, it is clear that present design show improvement in speed with reduction in used resources on target device.

<sup>7:</sup> end if

Value 100 ns 450 m 050 m 1300 me 1000100010101 0 3000 1000 10 10 100 1 10 10 100 1 30 10 10 10 10 datain(33.0) di. en light en brake en musik a dataout 🗑 d\_viper(63.0) 100000000000000 🔮 d, light(63.0) 1000000000000000 👹 d\_brake(63:0) 100000000000000 1000000000 (\$00) (\$00) 10 d\_music(63:0) 0000000000000 👹 dout(63:0) 10000000000000000 X1: 432.517 ns

Figure 7 shows RTL view of CAN top module.

Figure 8. Simulation Diagram of CAN Top Module

Figure 8 shows the simulation of CAN top which shows how algorithm work.

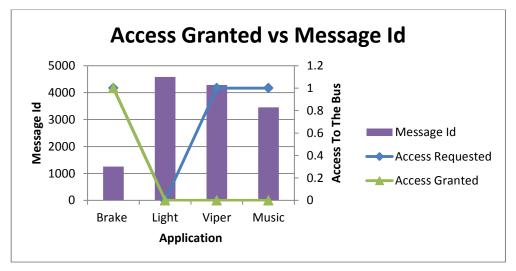

Figure 8. Graph of Access Granted vs Message Id

Figure 9 shows the graph between Access granted and Message Id. The above graph shows that the access is granted to the brake which has the minimum id value.

# 5. Conclusion

In this paper a novel algorithm for message scheduling in Control Area network is proposed which shows better results in term of speed and area optimization. In this work, dynamic message id allocation for emergency messages is tested and it is proved from the simulation results that whenever there is any emergency message then it immediately grants access to that message. A message scheduling in CAN is analyzed and evaluated in terms of randomness and biasness with the help of Xilinx 14.2 ISE tool. The simulation and synthesis of CAN has been performed on Modelsim6.3f. The area required has been measured in terms of slices, flip flops, LUTs, IOs and CLKs. The synthesis results shows that percentage utilization of number of slices has been found to be 18%, no. of flip flops – 10%, no. of IOs – 34%, no. of LUTs – 16% and no. of CLKs – 12%. As the no. of slices , flip flops , IOs increases ,complexity also increases. Speed has been calculated to be equal to 121.68 MHz with delay of 8.128 ns.

# References

- [1] L. Cauffriez, J. Ciccotelli, B. Conrarde, and M. Bayarte, "Design of intelligent distributed control systems: A dependability point of view", Reliab. Eng. Syst. Safety, vol. 84, (2004), pp. 19–32.

- [2] S. Kelkar and R. Kamal, "Control area network based quotient remainder compression-algorithm for automotive applications," in Proc. 38th Annu. IEEE IECON, Montreal, QC, Canada, (2012), pp. 3030– 3036.

- [3] M. J. Short and M. J. Pont, "Fault-tolerant time-triggered communication using CAN," IEEE Trans. Ind. Informat., vol. 3, no. 2, (**2007**), pp. 131–142.

- [4] J. R. Pimentel and J. A. Fonseca, "FlexCAN: A flexible architecture for highly dependable embedded applications," in Proc. 3rd Int. Workshop Real-Time Netw., Italy, (2004).

- [5] T. Fuhrer, B. Muller, W. Dieterie, F. Hartwich, R. Hugel, and H. Weiler, "Time triggered communication on CAN," in Proc. 7th Int. CAN Conf., Amsterdam, Netherlands, (2000).

- [6] H. A. Hansson, T. Nolte, C. Norstrom, and S. Punnekkat, "Integrating reliability and timing analysis of CAN-based systems," IEEE Trans. Ind. Electron., vol. 49, no. 6, (2002), pp. 1240–1250.

- [7] B. Jiang, Z. Mao, and P. Shi, "H∞-filter design for a class of networked control systems via T-S fuzzy-model approach," IEEE Trans. Fuzzy Syst., vol. 18, no. 1, (**2010**), pp. 201–208.

- [8] I. Broster, A. Burns and G. Rodríguez-Navas, "Probabilistic Analysis of CAN with Faults", In Proceedings of the 23rd IEEE Real-Time Systems Symposium (RTSS'02), (**2002**), pp. 269-278.

- [9] M. Di Natale, "Evaluating message transmission times in Controller Area Networks without buffer preemption", In 8th Brazilian Workshop on Real-Time Systems, (2006).

- [10] J. Ferreira, A. Oliveira, P. Fonseca and J. A. Fonseca. "An Experiment to Assess Bit Error Rate in CAN". In Proceedings of 3rd International Workshop of Real-Time Networks (RTN2004), pp. 15-18, Cantania, Italy, (2004).

- [11] T. Nolte, H. Hansson, and C. Norstrom, "Probabilistic worst-case response-time analysis for the Controller Area Network", In Proceedings of the 9th IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS'03), (2003), pp. 200-207.

- [12] S. Thales and V. Agarwal, "Controller Area Network (CAN) based smart protection scheme for Solar PV, fuel cell, Ultra-Capacitor and wind energy system based micro grid", *Photovoltaic Specialists Conference (PVSC)*, 2012 38th IEEE, IEESE, (2012).

### Authors

**Navdeep Parshar,** he has obtained his Bachelor of Technology degree from CT Institute of Engineering, Management and Technology, Jalandhar affiliated to Punjab Technical University in 2010, and Master of Technology degree from Centre for Development of Advanced Computing (CDAC) in 2012 respectively. He is currently serving as Assistant Professor in Bahra University Shimla Hills. He has published book on Cordic algorithm Techniques and many paper in the National & International journal and conferences. His area of interest is embedded system, VLSI design and testing, System on chip, DSP etc.

**Maandvi Sharma,** she received the B.Tech. (Electronics & Communication Engineering) degree from Swami Devi Dayal Institute of Engineering and Technology, Barwala affiliated to Kurukshtera University in 2012, and presently she is doing M.Tech. (VLSI Design) degree from Bahra University Shimla Hills and working on her thesis work her area of interest is low power VLSI design.