### EFFECT OF VARIATION OF GATE WORK-FUNCTION ON ELECTRICAL CHARACTERISTICS OF LIGHTLY DOPED PMOSFET

Nitin Sachdeva<sup>1\*</sup>, Tarun Kumar Sachdeva<sup>2</sup> and Neeraj Julka<sup>3</sup>

<sup>1\*</sup>Assistant Professor, J C Bose University of Science and Technology, YMCA Faridabad, Haryana, India

<sup>2</sup>Research Scholar, J C Bose University of Science and Technology, YMCA Faridabad, Haryana, India

<sup>3</sup>Research Scholar, Sant Longowal Institute of Science & Technology, Longowal, Sangrur

<sup>1</sup>nsymca81@gmail.com, <sup>2</sup>sachdeva.t@gmail.com, <sup>3</sup>neerajjulka@rediffmail.com

Abstract— Miniaturization of the dimensions of Metal Oxide Semiconductor field effect (MOSFET) transistors is very requisite nowadays for the enhanced enactment and integrated circuit compactness but this step of scaling arises to complications such as increased gate resistance and high leakage current. The utilization of integrated circuits in high-performance electronic gadgets is increasing day by day. As more and more complex functions are required in various fields like data/image processing and wired/wireless communication, the need to incorporate these functions in a compact package is also increasing. The reduction of channel length and other reduced parameters blemishes the device performance. The initial design can be designed and virtually fabricated in Computer-aided design (CAD) tool and the complexities of the design can be analysed at the early stage before the actual fabrication is done in fabrication laboratories. The scaling down of device dimensions results in a drastic increase in the sub-threshold leakage current of the device. There are various ways to reduce the leakage current of the device by increasing the work-function of the gate, variation of poly doping; halo doping and threshold implant concentration to reduce the leakage current of the device. To diminish these problems in Nano-scale transistors; there is massive interest in the variation of transistor's gate work-function. The experimental observations show that the devices with high gate work-function material have low leakage current as compared to low gate work-function devices. In this paper, 45nm P-MOSFET is virtually fabricated in ATHENA and simulated in ATLAS SILVACO. The workfunction of the gate of PMOS is varied from 5.05eV to 5.32eV to estimate the leakage current of the device. The simulation result shows that the 9.35 nA/µm is achieved at gate work-function of 5.25eV.

Keywords—PMOS, Athena, Atlas, Silvaco, CAD

### 1. INTRODUCTION

Down-scaling of feature size of field-effect transistor (FET) has provided a continued enhancement in rapid performance, package density and cost per transistor over the past few decades. While performing scaling, the transistor gate length becomes in Nano-meter

Received: April 10, 2019 Reviewed: May 14, 2019 Accepted: July 13, 2019

scale, problems related to MOS gate depletion and bigger gate resistance become more remarkable [1]. The depletion layer of the gate increases the equivalent gate oxide thickness and reduces the gate capacitance in the inversion regime [2]. There is a compromise between device performance due to a lesser inversion charge density and a lesser gate voltage. To reduce the problems of MOS gate depletion and bigger gate resistance, the active dopant density in the Poly gate material must be increased [3]. This can be done by increasing the gate work-function of the poly gate; by using the silicide material over the poly gates; by using the material with high work-function as the gate material [4, 5].

In this paper, work-function of gate material is set at different values to analyse the leakage current of the PMOS device. The MOS gate work-function is a very important consideration in the selection of gate materials for device integration because it directly affects the threshold voltage and performance of a transistor [6]. For bulk MOS transistors, the required gate work-functions for NMOS and PMOS transistors are close to the conduction and valence bands of silicon, respectively, to achieve low and symmetrical threshold voltages for optimal MOS performance [7]. The simulation results show that the raise of work-function of the gate of PMOS, the leakage current in the sub-threshold region of the MOS reduces [8].

### 2. DESIGN SPECIFICATIONS

By allowing the use of a lightly doped channel, significant benefits such as enhanced mobility and immunity to statistical dopant fluctuation can be achieved. Due to the low depletion charge density, work function engineering is utilized to adjust the performance metrics of the transistor. The operative work function of a gate material in a conductive—dielectric system is typically extracted from the flat-band voltage deduced from the capacitance-voltage characteristics of a metal-dielectric semiconductor capacitor[9].

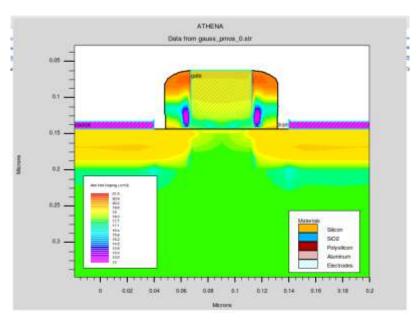

Fig. 1 Device Structure of PMOS in Contour Mode

A 45nm PMOS has been virtually fabricated in ATHENA package of SILVACO tool and simulated to analyze the current-voltage characteristics of the device in ATLAS package of SILVACO software. The fabrication is done by considering the optimum values of threshold implant concentration, halo implant concentration, and source/ drain

doping concentration. The fabricated structure of a 45nm PMOS is shown in Figure 1 above.

The effective gate length of 45nm PMOS is 40nm with an oxide thickness of 1nm. The N-type substrate is considered having 1e15 cm<sup>-3</sup> concentration and the supply voltage varies from 0.05V to 1.2V.

| _                 | · -                     |

|-------------------|-------------------------|

| Parameters        | Value Assumed           |

| Effective Gate    | 40nm                    |

| Length, Lg        |                         |

| Oxide thickness   | 1nm                     |

| Substrate         | 1e15 cm <sup>-3</sup>   |

| Pwell implant     | 7e13 cm <sup>-3</sup>   |

| Threshold implant | 2e12 cm <sup>-3</sup>   |

| Halo Implant      | 4e13 cm <sup>-3</sup>   |

| S/D doping        | 1 6e15 cm <sup>-3</sup> |

Table I. Specifications of 45nm P type MOS

Table I shown above specifies the parameters considered for the virtual fabrication of P-type device in ATHENA and by altering the concentrations of various parameters with different levels of dose in the ATHENA. ATLAS device simulator is incorporated to extract the current-voltage characteristics of the P-type device [10].

### 3. OUTPUT CHARACTERISTICS

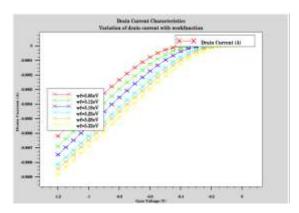

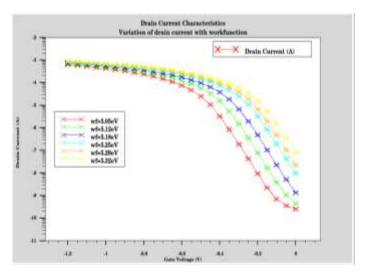

The output drain current is plotted w.r.t gate voltage at various work-functions. The poly gate work function has been varied from 5.05 to 5.32 eV. The transfer characteristics of PMOSFET have been shown in TONYPLOT of SILVACO in Figure 2 and Figure 3.

During the simulation, the gate voltage,  $V_G$  is varied from 0.05V to 1.2V at constant drain voltage to achieve the  $I_{DS}$ - $V_G$  curve. Afterward, the extracted parameters such as threshold voltage, ON current, OFF current, sub-threshold slopethe and DIBL has been extracted. To obtain  $I_DV_{DS}$  curve, the drain voltage,  $V_D$  was set to 0.1V to 1.2V at constant gate voltage. TONYPLOT of SILVACO is used to view the results in a graphical manner.

Fig. 2 I<sub>D</sub>-V<sub>G</sub> Curves in Linear Scale for multiple work-functions

Fig 3 I<sub>D</sub>.V<sub>G</sub> Curves in Log Scale for multiple work-functions

The sub-threshold characteristics of the device are efficiently improving by enhancing the work-function of the device. This is due to the fact that as the threshold voltage is increased by increasing the work-function, hence the leakage current in sub-threshold state decreases due to the increase of threshold voltage. The high threshold voltage is always required for fewer leakage currents in sub-threshold behavior mode [11].

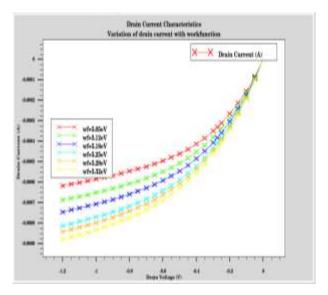

Fig. 4 I<sub>D</sub>-V<sub>D</sub> Curves for multiple work-functions

Figure 4 shows the deviation of drain current with drain voltage at different transistor's work-functions range. As the transistor's work-function increases, drain current of P-type MOS decreases.

# 4. INFLUENCE OF GATE WORK-FUNCTION ON VARIOUS PARAMETERS

There are various device and process parameters i.e threshold voltage, gate current, sub-threshold leakage current, drain current, mobility, trans-conductance, conductance, oxide thickness, etc. Among these parameters, the threshold voltage is an important parameter in MOSFETs.

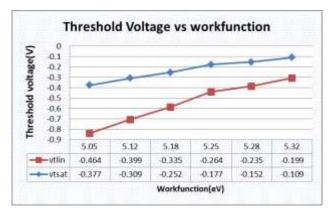

### 4.1. INFLUENCE OF GATE WORK-FUNCTION ON THRESHOLD VOLTAGE

The threshold voltage is the voltage required to turn on the MOS. It should be not altered in any conditions. Any change in it can alter the performance of the device. [12] It is directly proportional to the flat-band voltage, twice the bulk potential, and the voltage across the gate oxide due to the depletion charge and inversely proportional to the oxide capacitance expressed as in equation 1 below:

$$V_T = V_{FB} - \left| 2\phi_F \right| - \sqrt{\frac{2\varepsilon_S q N_d \left( \left| 2\phi_F \right| - V_{SB} \right)}{C_{OX}}} \dots \dots \dots \dots (1)$$

where, the flat-band voltage,  $V_{\rm FB}$ , is given in:

$$V_{FB} = \phi_{MS} - \frac{Q_f}{C_{ox}} - \frac{1}{C_{OX}} \int_{0}^{t_{ox}} \frac{x}{x_{ox}} \rho_{ox}(x) dx.....(2)$$

$\phi_F$  is the fermi potential, q is the charge of electron,  $C_{OX}$  is the oxide capacitance,  $V_{SB}$  is the source to bulk potential,  $N_d$  is the substrate doping,  $T_{ox}$  is the oxide thickness and  $\rho_{ox}$  is the charge density. The Fermi energy varies with the doping type and concentration. This gate's work-function is directly proportional to the electron affinity in the semiconductor and the difference between the conduction band energy and the intrinsic energy divided by the electronic charge. The changes due to gate work-function is represented by equation 3 below:

$$\phi_{MS} = \phi_{M} - \phi_{S} = \phi_{M} - \left(\chi + \frac{E_{g}}{2q} - |\phi_{F}|\right)....(3)$$

and

$$\left|\phi_{F}\right| = V_{t} \ln \frac{N_{d}}{n_{i}}$$

.....(4)

$E_g$  is the energy band-gap,  $n_i$  is intrinsic concentration and  $\chi$  is the electron affinity. The work-function is the amount of energy required to move from its Fermi level to free space. Due to difficulty defined in modeling, it is very challenging to theoretically predict the work function with accuracy. [13] The threshold voltage for gate work function ranging from 5.05eV to 5.32eV increases in the present simulation study. It has been analyzed that by enhancing the work function of MOSFET, the corresponding threshold voltage of the MOSFET will increase to the desired value. The threshold voltage for a PMOSFET device is negative.

Fig. 5 Threshold voltage Indicative curve

Figure 5 depicts the threshold voltage at two different drain voltages equals to 1.2V and 0.05V, rises with the rise of work-function of the gate of FET.[14] The Poly gate work function addiction of threshold voltage comes out to be linear relation, which can be verified through the equation (1). The result as depicted in this figure has been obtained for a P-type device having  $L_G$  =40nm, EOT=1nm and  $V_{\rm DD}$ =1.2V maintaining greater threshold voltage is a key requirement for low power devices and hence can be attained more proficiently by enhancing work function the gate material of PMOSFET device.

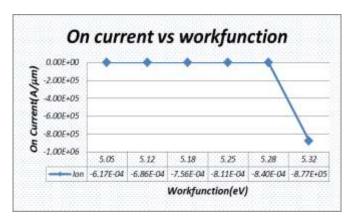

## 4.2. INFLUENCE OF TRANSISTOR'S WORK-FUNCTION ON DRAIN CURRENT AND SUB-THRESHOLD CURRENT

Both the drain current and subthreshold current cannot be achieved simultaneously in any device. So to achieve one best value of current among them should be foregone to achieve the best value of another current. The drain current variation of P-type MOSFET is shown as a function of the gate work function in Figure 6.

Fig. 6 Drain Current Indicative Curve

Figure 6 indicates the decrease of drain current with gate work-function parameter.

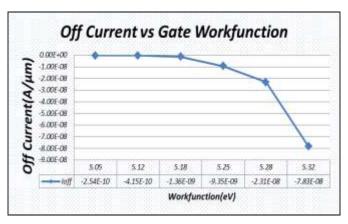

Fig. 7 Leakage Current Indicative Curve

The sub-threshold current characteristics showed that the best value is achieved at 5.25eV gate work-function Figure 7 is showing the variation of sub-threshold current with different work-functions.

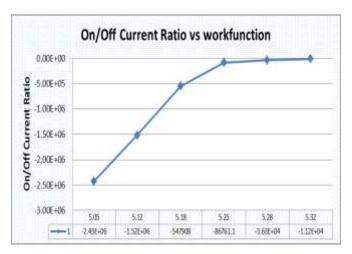

### 4.3. INFLUENCE OF TRANSISTOR'S WORK-FUNCTION ON ON/OFF RATIO

The On/Off ratio of current is the most important parameter to get the best performance device. The On/Off ratio of any MOSFET should be is in the range of e5 to

e6 which can be improved by increasing the work-function range. Different materials are used in the research labs nowadays to get the higher On/Off ratio. The variation of this current ratio with different work-function range is shown below in Figure 8.

Fig. 8 On/Off Ratio curve

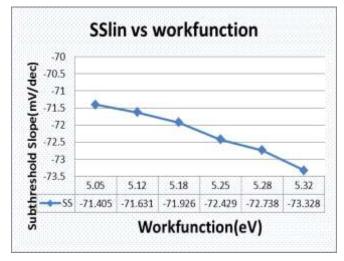

#### 4.4. INFLUENCE OF GATE WORK-FUNCTION ON SS

The lesser sub-threshold slope illustrates the fast switching of the transistor in the sub-threshold region. The sub-threshold region is that region where the leakage current flows due to minority carriers present in the MOS which is not required. But it can be reduced by increasing gate work-function of the P-type device[15]. The drain characteristic in addition to sub-threshold current is given below.

$$I_D \propto \exp\left(\frac{V_{gs}}{nN_T}\right)$$

....(5)

$$V_T = \frac{kT}{n}$$

$V_T = \frac{kT}{q}$  where  $\frac{kT}{q}$  k is the Boltzmann constant, T is the absolute temperature and q is the electron charge.

$$n = 1 + \frac{C_d}{C_m}$$

The subthreshold slope is given by:

$$S_{t} = \left(\frac{d(\log_{10} I_{ds})}{dV_{gs}}\right)^{-1} = 2.3 \frac{mkT}{q} = 2.3 \frac{kT}{q} \left(1 + \frac{C_{dm}}{C_{ox}}\right).(6)$$

where k is Boltzmann's constant and T is the temperature. The sub-threshold slope can be calculated by the known values of capacitances.

Fig. 9 Sub-threshold Slope Indicative Curve

The above Figure 9 shows that the decreased sub-threshold slope can be achieved with increased gate work-function of p-type MOSFET. The sub-threshold slope is the key parameter to achieve the fast switching and lesser leakage current in the sub-threshold regime.

### 5. CONCLUSION

The simulation-based analysis in this paper depicts the usefulness of work-function engineering for the regulation of various parameters in Nano-Scale devices. Also, with the increase of the transistor's work-function of the gate electrode, off-state leakage current of the device for lightly doped substrate decreases which is the necessary factor for low power applications. The On/Off current ratio increases and sub-threshold current decreases and sub-threshold behavior is also improved. After the exploration of all prerequisite parameters, it has been observed that by enhancing the threshold voltage, short channel effect decreases off state and the performance of the device increases. The sub-threshold leakage current and Sub-threshold slope are observed as  $9.35 \, \text{nA}/\mu \text{m}$  and  $72.42 \, \text{mV/decade}$  at a work-function of  $5.25 \, \text{eV}$ .

### ACKNOWLEDGMENT

We would like to yield this chance to express our appreciativeness to the Electronics Department, YMCA University of Science and Technology, Faridabad for their support and Lab facilities used to make this learning a successful

### REFERENCES

- [1] F. Salehuddin, I. Ahmad, F. A. Hamid, and A. Zaharim, "Application of Taguchi Method in Optimization of Gate Oxide and Silicide Thickness for," Int. J. Eng. Technol. IJET, vol. 9, no. 10, pp. 94–98, 2009.

- [2] J. Rozen, "Simulation of High Performance 35 nm Gate Length CMOS," pp. 1-7, 2004.

- [3] X. Li, S. a Parke, and B. M. Wilamowski, "Depleted SOI MOSFET," pp. 1–4, 1910.

- [4] "Future MOSFET Devices using high-k (TiO2) dielectric," Int. J. Res. Appl. Sci. Eng. Technol., vol. 1, no. II, pp. 23–28, 2013.

- [5] A. K. Anil Kumar, "Optimization of Threshold Voltage for 65nm PMOS Transistor using Silvaco TCAD Tools," IOSR J.Electron. Electron. Eng., vol. 6, no. 1, pp. 62–67, 2013.

- [6] K. A. Gupta, D. K. Anvekar, and V. V., "Modeling of Short Channel MOSFET Devices and Analysis of Design Aspects for Power Optimisation," Int. J. Model. Optim., vol. 3, no. 3, pp. 266–271, 2013.

- [7] S. Amin, M. Alam, and R. Khanam, "Design Consideration and Effect of Parameter Variation on sub-40nm Bulk MOSFET using TCAD Tool," Irphouse.Com, vol. 4, no. 3, pp. 267–274, 2011.

- [8] N. Sachdeva, M. Vashishath, and P. K. Bansal, "Analytical modeling & simulation of OFF-state

- leakage current for lightly doped MOSFETs," J. Nano- Electron. Phys., vol. 9, no. 6, pp. 1-4, 2017.

- [9] T. P. Dash, F. A. Ali, A. Sahoo, and G. Bose, "Study of 65nm n-MOSFET using SILVACO TCAD Study of 65nm n-MOSFET using SILVACO TCAD," no. January 2016, 2014.

- [10] N. M. Kasim, N. M. Saleh, L. M. Kasim, A. Ahmad, A. P. Ismail, and N. A. Ismail, "I D -V D and I D V G analysis of 45nm NMOS with strained silicon on insulator (sSOI) by using simulation," ISIEA 2014 2014 IEEE Symp. Ind. Electron. Appl., pp. 92–96, 2017.

- [11] F. Salehuddin, I. Ahmad, F. A. Hamid, A. Zaharim, H. A. Elgomati, and B. Y. Majlis, "Analyze of input process parameter variation on threshold voltage in 45nm n-channel MOSFET," 2011 IEEE Reg. Symp. Micro Nanoelectron. RSM 2011 - Program. Abstr., pp. 70–74, 2011.

- [12] H. A. Elgomati, B. Y. Majlis, F. Salehuddin, I. Ahmad, A. Zaharim, and F. A. Hamid, "Optimizing 35nm NMOS devices V TH and I LEAK by controlling active area and halo implantation dosage," 2011 IEEE Reg. Symp. Micro Nanoelectron. RSM 2011 Program. Abstr., pp. 286–290, 2011.

- [13] N. Ali, D. Dheer, S. Paliwal, and C. Periasamy, "TCAD analysis of variation in channel doping concentration on 45nm Double-Gate MOSFET parameters," 12th IEEE Int. Conf. Electron. Energy, Environ. Commun. Comput. Control (E3-C3), INDICON 2015, no. December 2015, 2016.

- [14] N. Shashank, S. Basak, and R. K. Nahar, "Design and Simulation of Nano-Scale High-K Based MOSFETs with Poly Silicon and Metal Gate Electrodes," Int. J. Adv. Technol., vol. 1, no. 2, pp. 252– 261, 2010.

- [15] U. C. Berkeley, "CHAPTER 6: Parameter Extraction," BSIM3v3.2.2 Man., pp. 1–18, 1999.

International Journal of Future Generation Communication and Networking Vol. 12, No. 4 (2019)